Teledyne e2v: Boost dynamic performance of a broadband ADC by some 10 dBFS instantly with spur reduction IP

- Written by Auzzi Shopping

Benefit from an immediate design-free, dynamic performance gain

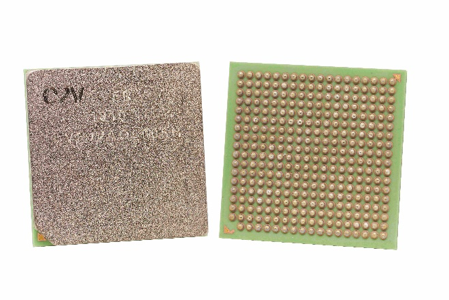

- The new EV12AQ600/605-ADX4 device options now feature an integrated ADX4 license key enabling enhanced dynamics when operating at up to a peak of 6.4 GS/s (single channel mode).

- ADX4 - a post-processing algorithm compatible with Xilinx Kintex® Ultrascale™ FPGAs delivers up to 10 dBFS of SFDR dynamic spurs reduction and close to 1 effective bit extra resolution in broadband applications.

- Time-interleaving, whilst providing a conceptually easy to comprehend sample rate boost, is challenging to achieve at extended resolutions and wide bandwidths.

Gain immediate, design-free access to a dynamic boost for the EV12AQ600/5

GRENOBLE, FRANCE - Media OutReach - 17 June 2022 - Teledyne e2v today announces the immediate availability of EV12AQ600/5 models featuring an integrated license key providing direct access to the novel ADX4 post-processing algorithm developed at SP Devices within the Teledyne group of companies. The ADX4 spur reduction IP dynamically attenuates spurious frequency components resulting from gain, offset and phase mismatches between the four ADC cores. Time-interleaving is a trusted architectural approach to boost ADC sampling rates. However, avoiding resulting spectral artifacts with calibration is especially challenging beyond 10-bit resolutions and in broadband applications.

Applied to the EV12AQ600/5, time-interleaving four cores quadruples the sample rate from 1.6 to 6.4 GS/s. The mismatche errors between the ADC coresreduce spurious free performance. ADX4 delivers a spurious free dynamic range (SFDR) boost of up to 10 dB. That boost is particularly noticeable in broadband applications, and as it requires no hardware design changes is available on demand. The ADX4 code module is simply programmed into the post-processing FPGA. A modification that can even be retrofitted in the field.

About ADC time-interleaving

High-resolution data converters are on an upward trajectory to acquire broader instantaneous bandwidths. A theoretically simple method to achieve higher sampling is by applying time-interleaving to existing cores. Here, multiple ADC cores are clocked on different phases of a common sample clock allowing a higher density of samples of a signal to be acquired. This increased sample density offers a useful performance extension and works well with modest resolutions up to 8-bits in which cross core matching is relatively easy to manage through standard mixed signal calibration and circuit layout schemes.

For 10-bit resolutions and above, especially operating into the gigahertz range, it is increasingly hard to ensure matching. As a result, sampling artifacts arise causing distortion and limiting measured dynamic performance. These high frequency mismatch errors are very challenging to mitigate in the analog design domain. Consider that, for a 6.4 GS/s time-interleaved ADC to achieve 72 dB SNR (the theoretical 12-bit maximum) with a 3 GHz input signal, a cross core phase match of better than 12 fs is required.

Thankfully, over the last two decades, the cost of DSP resources has fallen significantly, now making it economically feasible to take an algorithmic approach to spur reduction. Teledyne SP Devices, the home of high resolution ultra-fast digitizers is well versed in mitigation technologies with experience gathered from several decades work on a broad range of industry leading discrete converters.

Unlike a single or multi-point calibration, ADX4 digital error correction can deliver spur suppression even when the errors vary over frequency. Results are such that the unwanted aliasing spurs are suppressed into the noise floor.

Implementing ADX4

It could not be easier to gain ADX4 dynamic enhancements. Via the desired supply chain, customers need only transition their orders across to the -ADX4 options of their EV12AQ600/5 device. Moreover, they need to add the ADX4 module to their Xilinx FPGA code load. Job done.

ADX4 availability

The following component list indicates the current EV12AQ600/5 options shipping today with ADX4 license keys. Customers considering dual channel operation should contact Teledyne e2v directly to discuss the future availability of an ADX2 license key option.

Useful links

Teledyne e2v EV12AQ600/5-ADX4 datasheet

Teledyne e2v EV12AQ600/5 product page

Video link: Learn time-interleaved EV12AQ600 ADC mismatch error correction

About Teledyne e2v

Teledyne e2v’s innovations lead developments in healthcare, life sciences, Space, transportation, defense and security and industrial markets. Teledyne e2v’s unique approach involves listening to the market and application challenges of customers and partnering with them to provide innovative standard, semi-custom or fully custom solutions, bringing increased value to their systems.

#Teledynee2v

About Teledyne SP Devices

Teledyne SP Devices designs and manufactures world-leading modular data acquisition and signal generation instruments. Their products utilize patented calibration logic, the latest data converters, and state-of-the-art FPGA technology resulting in an unrivaled combination of high sampling rate and resolution. Products are available with a range of application-specific features and embedded, real-time signal processing. This helps customers overcome performance bottlenecks, shortens time-to-market, and provides system-level advantages within a wide range of application areas. SP Devices' products are deployed across a wide variety of industries, including analytical instruments, remote sensing, scientific instrumentation, medical imaging, and more. For more information, visit SP Devices' website at www.spdevices.com.